2021年3月号

Focus on the News

量子コンピュータの小型化・高速化を実現する回路圧縮手法を開発

国立情報学研究所とNTTは、大規模な量子コンピュータ上の計算回路の圧縮化とコンパイラ設計のための新しいアプローチを定式化しました。本手法を用いることで、量子計算サブルーチン回路を平均約70%圧縮することが可能となり、大規模量子コンピュータの開発に必要とされるリソースの低減化を実現しました。大規模量子コンピュータに必要とされる量子ビット数の大幅な削減と、計算時間の短縮化による量子コンピュータの高速化が期待されます。

本研究成果は、Phys. Rev. Xに米国東部時間2020年11月11日に掲載されました。

■概要

将来開発が期待される大規模な量子コンピュータは、ユーザが量子コンピュータに入力する量子アルゴリズムから、量子コンピュータ内のハードウェア動作までの間に、コンパイルと最適化が何段階にもわたって行われると考えられています。また、このような大規模な量子コンピュータは誤り耐性型汎用量子コンピュータとも呼ばれ、誤りに耐性を持つ符号化の構造を持つことを特徴としており、誤りに耐性を持つ符号へのコンパイルや最適化の手法の開発が、大きな課題の1つとなっていました。この誤り耐性のある符号化のうち、量子コンピュータの設計にもっとも多用されているのはトポロジカル符号で、中でも特に代表的なのは、超伝導量子ビット実装の2次元表面符号と、主に分散型の量子コンピュータの設計に用いられる3次元トポロジカル符号です。本研究では、これらのトポロジカル符号を統合化し、量子計算回路における最適化を通して、量子コンピュータの誤り耐性実装に伴う大規模なオーバヘッドの低減と、コンパイラ設計の中心となる量子コンピュータ言語への新しいアプローチを提案しました。

■本研究成果

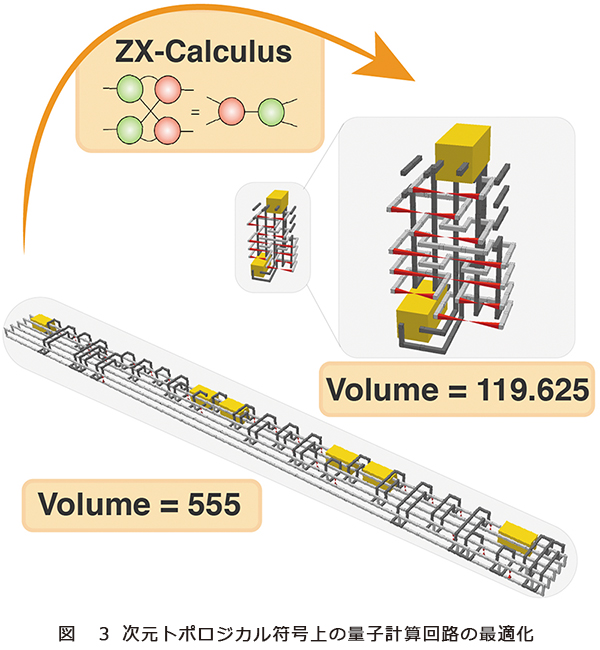

本研究では、まず、ZXカリキュラスを3次元トポロジカル符号上の量子計算回路に応用し、ZXカリキュラスの持つ演算機能を用いて量子計算回路の圧縮化を行いました。3次元トポロジカル符号では、論理量子ビットを定義するために挿入されたディフェクトと呼ばれる構造が絡み合うことでトポロジーを変え、演算を実装するために、量子計算回路を絡み合うパイプ構造として3次元的に視覚化することができます。このパイプ構造がつくる体積を圧縮することにより、量子計算回路の圧縮化が達成されます。本研究では、よく使われる量子回路のサブルーチンに対して本手法を用いることにより、平均で約70%の圧縮率を達成することに成功しました。量子計算回路を圧縮した分、量子コンピュータに必要とされる量子ビット数を削減できるだけでなく、量子計算回路の実行時間を短縮化できるため、量子計算を高速化できます。

■研究の詳細

これまでの3次元トポロジカル符号上の量子計算回路の圧縮は、パイプ構造の変形法則が不完全であることから、圧縮過程で量子計算回路まで変えてしまうなどのさまざまな問題を含んでいました。これらの問題から、2次元表面符号の方が量子計算回路の圧縮に適しており、優れた性質を持つとの考えが定説となっていました。

本研究ではまず、3次元トポロジカル符号上の量子計算回路の圧縮が回路の性質を変えてしまう問題を回避するため、論理ゲートの変形法則が定式化されているZXカリキュラスに注目し、ZXカリキュラス上で回路の圧縮を行うことにしました。ところが、ZXカリキュラスと3次元トポロジカル符号上の量子計算回路表現(パイプ構造)の間の関係性が解明されていなかったため、この関係性を明らかにし定式化する必要がありました。本研究では、ノードのテンソルネットワークとして表現されるZXカリキュラスに、従来とは異なる新しい解釈を導入することで、3次元トポロジカル符号上のパイプ構造との間に新しい関係性が成り立つことを初めて発見することに成功しました(図)。

ZXカリキュラスを中心に、2次元表面符号と3次元トポロジカル符号の量子計算回路を統合することで、従来の定説を覆し、3次元トポロジカル符号での高い回路圧縮が可能であること、また2つの符号化をハイブリッドしたより効率的な圧縮方法が可能であることを示しました。具体的な例として、多用される量子計算サブルーチンの圧縮に本手法を用いて、従来方法での圧縮回路よりさらに圧縮度の高い量子計算回路を得ることで、手法の有用性を示しました。圧縮後の量子計算回路は、ZXカリキュラスと3次元トポロジカル符号上の量子計算回路表現間の関係をコンパイルに用いて、ハードウェアに回路実装することができます。

■将来的な展望

量子コンピュータに実装される量子ビットの数は年々増えていますが、量子コンピュータの本格実用化には、エラーの克服が最重要課題となっており、世界的に誤り耐性を特徴とする大規模量子コンピュータの登場が期待されています。本手法を用いて誤り耐性の実装に必要とされるリソース負荷を低減することにより、より早い大規模量子コンピュータの実現が期待できます。3次元トポロジカル符号に基づく大規模量子コンピュータの制御性の改善とリソースの低減を大幅に進めることができたことは、分散性のあるネットワーク的な量子コンピュータの可能性を飛躍的に高めるものでもあり、NTTが進めるIOWN (Innovative Optical and Wireless Network)構想の実現に向けて量子技術からのアプローチを加速するものです。

また、大規模量子コンピュータを設計するうえで、本手法は量子コンピュータアーキテクチャと合わせて中心的な位置を占め、命令制御アーキテクチャやコンパイラの設計の基礎としての役割を担っていくことが期待されます。

研究者紹介

誤り耐性量子コンピュータのためのコンパイラとは

根本 香絵

国立情報学研究所

量子情報国際研究センター

情報学プリンシプル研究系

量子コンピュータの中で情報処理をするとき、その情報は多数の量子ビットがつくる量子状態に格納されています。量子状態はとても壊れやすいので、量子コンピュータの中で処理される量子情報もまた、ノイズによって大きな影響を受けます。そのため、量子コンピュータのサイズを大きくしたり、難しい問題を長い時間かけて計算するためには、誤りに対して耐性を持たせることが必要です。誤りに対して耐性を持つ量子コンピュータは、誤り耐性量子コンピュータと呼ばれ、量子コンピュータ開発の中でも長期的な課題で、この開発へ向けて現在研究が活発化しています。誤り耐性量子コンピュータではまず、量子誤り訂正符号を用いて論理量子ビットをつくり、この論理量子ビット上に論理量子ゲートを誤り耐性実装することで、誤り耐性のある量子情報処理が実装されます。数多くの量子ビットから守られた量子ビットを1つつくるという冗長性だけでなく、量子論理ゲートを誤り耐性実装することに非常に大きな物理的リソースが必要になるため、全体として誤り耐性量子コンピュータはとても大きな装置となります。

今回私たちはNTT物性科学基礎研究所と共同で、誤り耐性量子コンピュータ中で実行される量子回路の形式化を、ZXカリキュラスを用いて行い、この形式化が量子誤り訂正符号の違いを超えて共通の形式として用いることができることを示しました。この新しい方法を、サブルーチン量子回路の圧縮化に用いることで、誤り耐性量子コンピュータの高速化や必要となるリソースの大幅な低減化を可能にしました。本研究成果は、誤り耐性量子コンピュータの実装を早めるだけでなく、コンパイラ設計の中心となる量子コンピュータ言語への新しいアプローチを提案するもので、将来のコンパイラの設計や量子コンピュータ言語の基礎として重要な役割を持つと考えています。

研究者紹介

誤り耐性量子コンピュータの量子回路圧縮

William John Munro

NTT物性科学基礎研究所

量子科学イノベーション研究部 理論量子物理研究グループ

理論量子物理研究センタ

量子力学の原理は新しいICTを可能にし、現在のICTに革命的な発展をもたらすと期待されています。そのような量子デバイスの開発によって、現在の技術では困難な問題や取り扱いが不可能な問題までも解くことができると予想されています。現在までに、50から100量子ビット程度のNISQデバイスが開発されています。NISQデバイスのNはnoisyを意味し、その名前のとおりノイズのある量子デバイスです。これらNISQデバイスを用いて、従来のコンピュータでは計算するのが難しいほどの複雑性を生みだすことができることがすでに示されています。ただし、ノイズがあるということは、量子計算に大きな制限があるということで、難しい問題や、大きな(多数の量子ビットを必要とする)問題は解くことができません。この制限を受けないようにするには、誤り耐性量子コンピュータの開発が必要です。誤り耐性量子コンピュータの開発は、量子コンピュータ開発における究極的な目標で、想像もできないような問題をも解くことができるようになると考えられている一方、NISQデバイスが実現している量子ビット数の100万倍もの数の量子ビットを必要とします。NISQデバイスと誤り耐性量子コンピュータの間にある、この大きなギャップを橋渡しすることが必要です。2020年11月に私たちは、量子プログラムを実行するのに必要とされる論理量子ゲートと量子ビットの数を大幅に低減する、誤り耐性量子コンピュータのための量子回路圧縮方法を提案しました。私たちの研究成果は、誤り耐性量子コンピュータの実現を早めることに寄与するもので、米国物理学会のPhys. Rev. X誌に掲載されました。量子回路の圧縮を自動化しやすいことと、圧縮後の量子回路の検証が自然にできることも、この方法の優れた点の1つです。

この研究成果は、国立情報学研究所のMichael Hanks博士、Marta Estarellas博士、根本香絵教授との共同研究で、Q-LEAP基礎基盤研究の支援を得ています。本研究では、物理学、工学、コンピュータ科学、そして化学と、非常に多様な分野背景を持つ研究者が参加しています。私たちが開発した方法は、量子コンピュータ設計やその実装研究のさらなる発展を活性化していくものと思います。