2023年9月号

特集

超伝導量子コンピュータのシステムの設計と開発

- 量子計算

- 超伝導量子ビット

- 計算機アーキテクチャ

これまでに実現されてきた量子コンピュータをより大規模で実用的なサイズへ拡大しサービスとして提供するには、たくさんの量子ビットを制御可能にする方法と動作を記述する抽象化が必要となります。本稿では、2023年3月にローンチされた量子コンピュータにおける、量子ビットを制御しクラウドサービスとして利用可能にするまでの取り組みや難しさ、また、クラウドサービスの仕組みや今後の展望について解説します。

鈴木 泰成(すずき やすなり)

NTTコンピュータ&データサイエンス研究所

はじめに

量子コンピュータは量子的な物質の重ね合わせ状態を計算に活用し、高速な演算や新たな情報処理の実現に寄与すると期待されています。一方、重ね合わせ状態は環境のノイズに弱く簡単に情報が変化してしまうことから、従来の量子計算の研究は重ね合わせ状態を長時間保持できるデバイスの探求、量子的なノイズを削減するための符号理論などの探索、理想的な量子コンピュータで効率的に実行できるアルゴリズムや計算性能の限界の解析などが主でした。近年ではこれらの基礎技術が確立されてきたことから量子計算の実現が現実味を帯びるようになり、その成果を組み合わせ大規模な量子コンピュータを具体的に設計、開発する取り組みが盛んに行われるようになっています。NTTは、理化学研究所らと共同で超伝導量子ビット*1を用いた集積化された量子コンピュータの開発に取り組み、2023年3月に国内初の量子コンピュータクラウドサービスをローンチしました。量子コンピュータの開発にはさまざまな技術が必要となりますが、NTTはこの中で特に量子ビットのキャリブレーションと、制御を抽象化および自動化しクラウドサービスとして提供できるようにする技術開発に取り組んできました。本稿では、超伝導量子コンピュータの概要と、実用的な量子計算の実現に向けた計算機の開発に向けた取り組みについて解説します。

*1 超伝導量子ビット:超伝導状態にある回路を用いて量子ビットの0,1を表現するデバイス。集積性を確保しながら高い精度で制御可能なことが知られており、拡張可能な量子コンピュータを実現する主要な候補と考えられています。

超伝導量子ビット

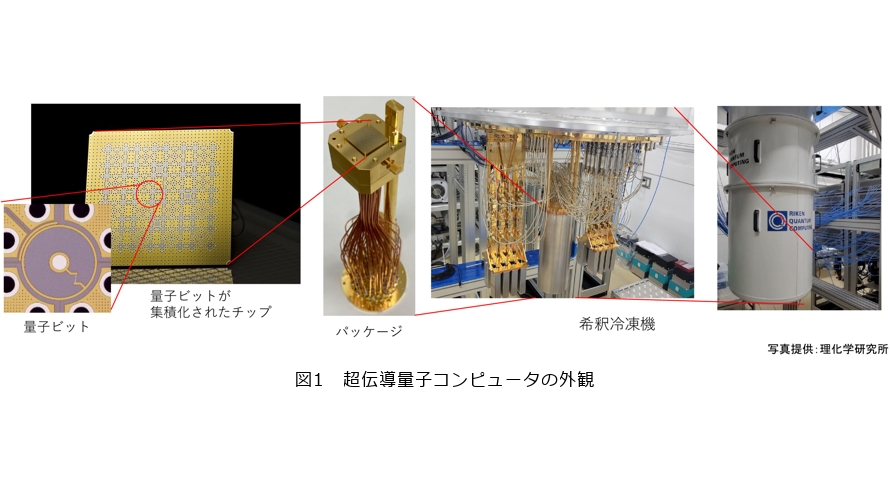

私たちの身の回りにある物質は量子力学に従っているため、識別可能などのような2状態も理論上は重ね合わせ状態にして量子ビットとして扱うことができます。一方、私たちが現実的に重ね合わせ状態を長時間維持できるシステムは限られています。超伝導回路を用いて設計したデバイスのもっともエネルギーが小さい識別可能な2状態を量子ビットとして用いる超伝導量子ビットは、基盤の上に集積化可能で数百マイクロ秒からミリ秒程度の長い寿命を維持できることから、拡張性の高い量子デバイスとして期待されています。図1は量子ビットが集積化されたチップの写真で、左図にある円形の回路が1つの量子ビットに対応します。この量子ビットは2次元的にチップ上に並べられ、パッケージを介して外部まで配線されています。超伝導量子ビットの重ね合わせ状態は熱に弱いため、チップは希釈冷凍機を用いて数十ミリケルビンまで冷却されます。

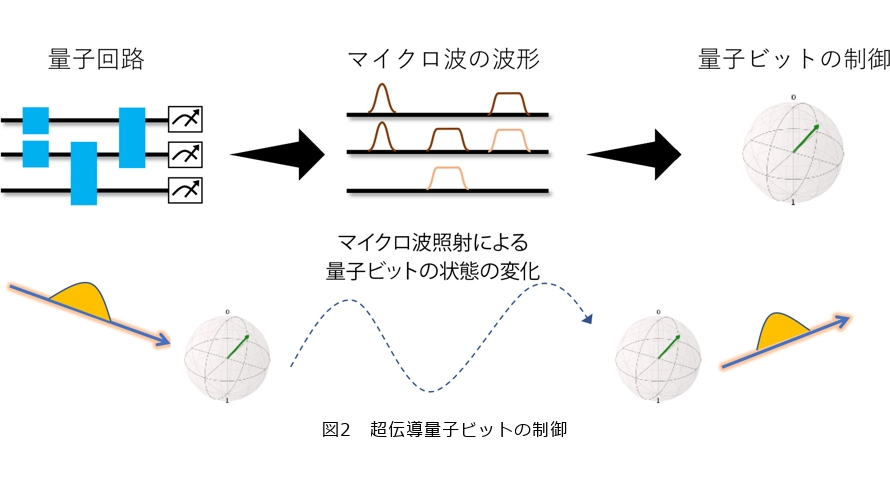

図1に表示される超伝導回路そのものは情報を保持する媒体であり、それ自身は計算する能力を持ちません。このため所望の情報処理をするには、図2のように量子ビットにマイクロ波を照射して制御する必要があります。典型的な量子計算のプログラムは量子回路と呼ばれる論理回路を模した表現で記述されます。量子回路における量子ビットに対する操作は、ユニタリ操作と呼ばれる量子ビットの情報を得ずに量子状態を変化させる操作と、読み出し操作と呼ばれる量子ビットの状態が0と1のどちらかを取得する操作の2種類からなります。このどちらの操作も、量子ビットの特性と操作の種類に応じて最適化された形状のマイクロ波を複数照射して行います(1)。読み出し操作の場合はこれに加え、量子ビットから返ってくるマイクロ波の形状を調べ、形状から状態が0か1かを判定する必要があります。

量子ビットを制御するマイクロ波の照射と読み出しは実験的には次のように実現されます。まず、通常の計算機を用いて量子回路の要素や量子ビットの特性に合わせ、マイクロ波の形状をデジタルなデータとして設計します。次に、このデータを室温に配置されたエレクトロニクスに転送し、エレクトロニクスはデジタルな信号をアナログな信号に変換してマイクロ波を出力します。マイクロ波は配線を通して希釈冷凍機の中の量子ビットに伝送され、量子ビットに操作が行われます。量子ビットの状態を読み出す場合は量子ビットから返ってくる信号を計測し、エレクトロニクスでアナログな波形をデジタルなデータに変換します。最後に、デジタルな波形データに対する2値識別の判定を行うことで、測定結果が0と1のどちらであったのかを判定します。並べられた量子ビットに対してこれらの処理を実施することで、所望の計算を行い、結果を取得することができます。

量子ビットの制御

量子ビットを用いて量子計算を行うには、量子ビットで所望の制御をするのに必要なマイクロ波のパルス形状や、読み出し操作に際する2値識別の関数を設計しなければいけません。最適なパルスの形状は量子ビットの寿命やエネルギー差といった特性に依存しており、これらの特性は量子ビットごとに異なるため、制御信号は個別に設計する必要があります。また、量子ビットの特性は設計した段階である程度推定が可能ですが、正確な値は実験的に評価しなければ分かりません。このため、量子ビットで計算をできるようにするには、まず希釈冷凍機で冷やした後に複数回の測定を通して量子ビットの特性を明らかにし、次に特性から最適なパルスの形状や読み出し操作の識別関数を量子ビットや量子回路での操作の種類ごとにつくる必要があります。このように、製造した量子ビットが計算に利用できるように行う一連の実験をキャリブレーションと呼びます。

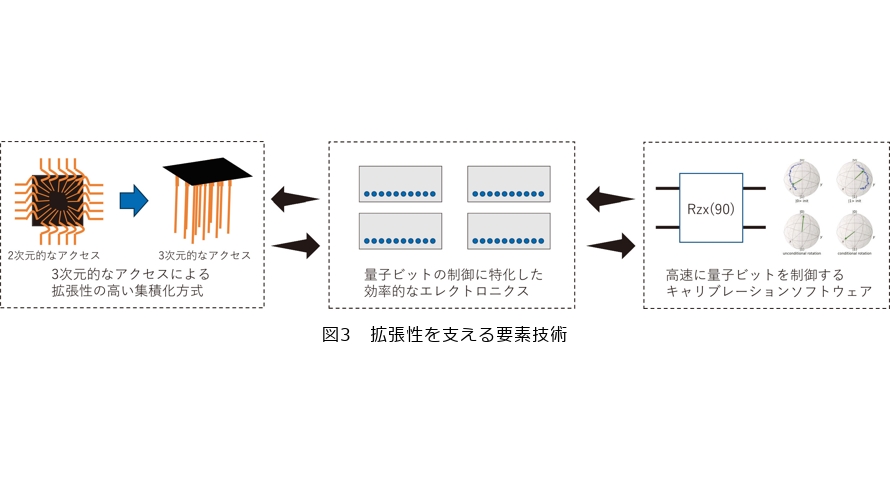

量子ビットのキャリブレーション自体は従来の少数の量子ビットの実験でも行われてきました。しかし、1、2個の少数の量子ビットを制御することができても、単純に大規模化していくと少数の量子ビットを扱っていたときには気にならなかった事項が問題となります。大規模な量子コンピュータを実現するには、実際に大規模な量子計算を構築して拡張性を阻害する課題を実験的に発見し、これを1つずつ取り除かなければなりません。ここでは図3に示される量子計算の拡張性を支える3つの要素技術について紹介します。

量子コンピュータを拡大するにあたり最初に課題となるのが量子ビットの配線の問題です。典型的には量子ビットはチップの上に2次元的に並べられ、個々の量子ビットに制御信号を伝送するため、チップの周辺から個別に配線されます。しかし、この方式を採用すると必要な配線の数はチップの一辺の2乗で増えていく一方、配線可能な本数はチップの一辺の4倍でしか増えないため、規模がある程度大きくなると配線が難しくなってしまいます。この問題を解決するため、今回の量子コンピュータでは理化学研究所がチップに対して3次元的に制御線を配線する拡張性の高い方式を提案し、富士通株式会社、産業技術総合研究所、情報通信研究機構とともにこの方式での集積化を実現しています(2)。2番目の課題がエレクトロニクスの効率化です。できるだけ少ない配線で量子ビットを効率的に制御するためには、複数の周波数や波形のマイクロ波信号を多重化して送出する必要があります。これを実現するために量子ビットごとに高価な計測装置を導入すると、量子ビットの数が増えるにつれコストやサイズの観点で拡張が現実的ではなくなります。今回のシステムでは、大阪大学らが主導して開発した量子ビットの制御に最適化されたエレクトロニクスが利用されています。最後に課題となるのが量子ビットを制御し効率的にキャリブレーションを行うソフトウェアの構築です。先述したように量子ビットの特徴付けを手作業で行う方法自体は知られていますが、大量の量子ビットを1つずつ手作業で調整することは現実的ではありません。また、量子ビットや制御装置の特性は時間とともに変化するため、時間をかけてキャリブレーションしていては正確な操作ができません。NTTと理化学研究所は、複数のエレクトロニクスを並列に制御し量子ビットを体系的に計測する基盤を構築しました。また、この基盤を用いて複数の量子ビットを並列かつ正確にキャリブレーションするためのソフトウェアや自動化のためのプロトコルを構築しました。

システムの抽象化と運用

前述のシステムで集積化された量子ビットを制御するための基盤技術はそろいましたが、これをクラウドサービスとして持続的に運用するには、安定した稼動を維持するためのノウハウの構築と、ユーザに提供するためのサービスの仕組みづくりが必要となります。前述の構築した計測のためのインフラは、量子ビットが理想的に製造された際には問題なく動作しますが、実際にはさまざまな理由でキャリブレーションが失敗してしまうことがしばしばあります。この失敗の要因は配線ミスといったヒューマンエラーから、量子ビットの特性が設計値から大きく外れてしまい制御できないという製造の問題まで多岐にわたります。システムが大規模化するとその要因の種類や個所の特定自体が困難となり、現実的な運用が難しくなります。このため、全体を統括するソフトウェアは正常系で正しく動作するだけでなく、異常が生じた際にその原因をできるだけ早い段階で正確に報告できることが期待されます。異常なケースの分類は無数にあるため、これを完全に自動化することは容易ではありませんが、開発の期間でノウハウを蓄積し典型的な要因を効率的に見出す体制を構築しています。

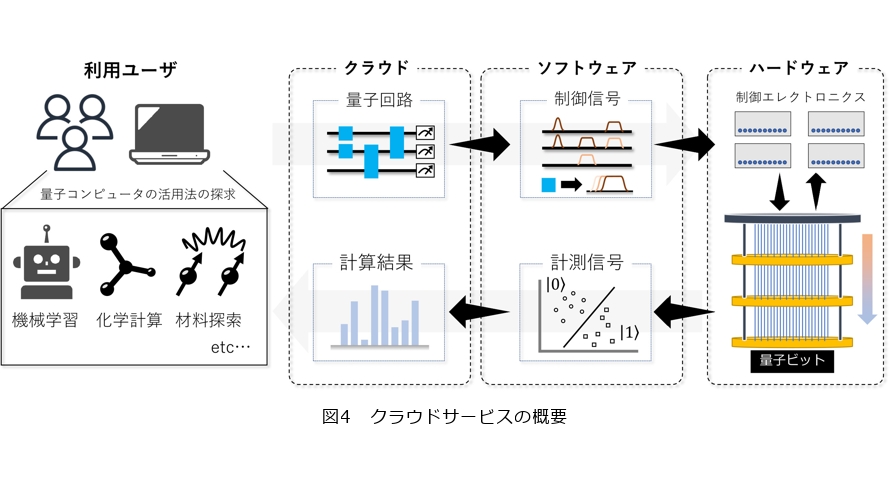

構築したシステムをサービスとして提供するには、ユーザが計算機を利用しやすくするためのWebサービスの構築も必要です。現在の設計では量子ビットを制御するもっとも低レベルなプログラムの表現は、量子ビットを制御するマイクロ波の波形情報です。この表現は量子ビットの特性を調べる実験などでは便利ですが、ユーザが行いたい計算をユーザにパルス形状で記述させることは現実的ではありません。今回の計算機のインフラでは、キャリブレーションが完了していない状態でパルスの形状を直接設計するジョブの記述方式と、キャリブレーションが完了した後に量子回路の描像でプログラムを指定する方式の2つの方式を提供しています。今回提供されるクラウドサービスでは、大阪大学、理化学研究所、NTTが連携し、図4のように、ユーザは量子回路で記述したプログラムをフロントエンドで受け止め、バックエンドのサービスで後者の方式を用いて量子ビットを用いた計算を行い、計測データを識別した測定値をユーザに返却するという仕組みを構築しています。

今後の展望

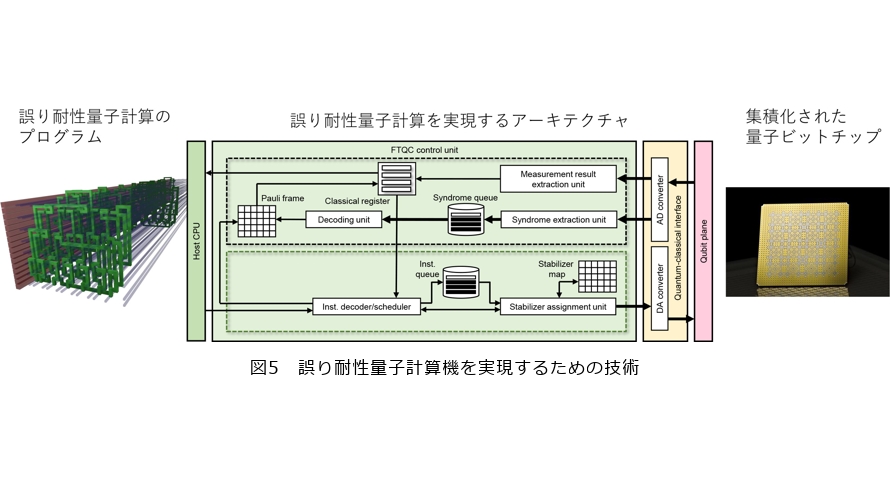

現在のクラウドサービスは量子ビット集積化の1つの到達点ではありますが、実用的な量子コンピュータを実現するにはまだ多くの壁を乗り越えねばなりません。図5に示されるように、NTTではこうした将来の実用化に向けた技術開発を並列して進めています。現在の計算機の最大の問題点はその大きなノイズにあります。現在実現されている量子ビットはもっとも良いものでもゲート操作をするたびに0.1%程度の確率でエラーが生じるため、大規模な量子アルゴリズムを信頼性のあるかたちで実行することができません。そこで、量子誤り訂正技術*2を用いて量子ビットを符号化し、計算中に誤りを逐次的に訂正することで誤り率を実行的に小さくする技術の実現が期待されています(3)。また、誤り訂正が実現すれば、量子ビットのエラーや特性のばらつきをある程度まで誤り訂正で吸収できるようになるので、アーキテクチャを慎重に設計することで拡張性に優れた計算機を構築できます。NTTはさまざまな研究機関と連携し、量子誤り訂正を実現するための計算機アーキテクチャを具体化しています(4)〜(8)。誤り訂正を前提としたアーキテクチャを構築すると、私たちが実行できる基本命令セットはデバイスよりもむしろ誤り訂正符号の特性で規定されるようになります。このため、誤り耐性量子コンピュータをターゲットにしたコンパイラやソフトウェアも新たに必要になります。NTTでは、誤り耐性量子計算で実行するような長期的な誤り耐性量子計算を見据えたコンパイラを構築し、これを最適化するための手法や評価するためのソフトウェアを提案してきました(9)(10)。図5の左には、実際に設計したプログラムがコンパイル最適化の途中で3次元的なグラフとして表示されている様子を表しています。

次なる目標は、これまでに構築したこうしたシステムスタックを量子ビットと融合させ、誤り耐性のある量子コンピュータの実証をすることです。誤り訂正を取り入れ、計算機として高速に命令が処理できるようなシステムをつくるには、今まで以上に物理と計算機科学の融合が必須となります。NTTはこうした横断分野でのソフトウェアとハードウェアが一体となった協調設計に基づく計算機のデザインを探求し、実用的な量子コンピュータの未来を世界に先駆けて描き出していきます。

*2 量子誤り訂正技術:誤り率が小さな量子ビットを複数用いて少数の論理的な量子ビットを表現することで、論理量子ビットに生じる誤り率を実効的に削減する技術。

■参考文献

(1) P.Krantz, M.Kjaergaard, F.Yan, T.P. Orlando, S.Gustavsson, and W.D. Oliver:“A quantum engineer's guide to superconducting qubits,”Appl. Phys. Rev.,Vol.6,No.2,021301,2019.

(2) S.Tamate, Y.Tabuchi, and Y.Nakamura:“Toward Realization of Scalable Packaging and Wiring for Large-Scale Superconducting Quantum Computers,”IEICE Transactions on Electronics,Vol.E105.C,No.6, pp.290-295,2022.

(3) A.G. Fowler and C.Gidney:“Low overhead quantum computation using lattice surgery,”arXiv preprint arXiv:1808.06709,2018.

(4) Y.Suzuki, Y.Ueno, W.Liao, M.Tanaka, and T.Tanimoto:“Circuit Designs for Practical-Scale Fault-Tolerant Quantum Computing,”2023 Symposium on VLSI Technology and Circuits, 2023.

(5) W.Liao, Y.Suzuki, T.Tanimoto, Y.Ueno, and Y.Tokunaga:“WIT-Greedy: Hardware System Design of Weighted ITerative Greedy Decoder for Surface Code,” 28th ASP-DAC 2023, pp. 209-215,2023.

(6) Y.Suzuki, T.Sugiyama, T.Arai, W.Liao, K.Inoue, and T.Tanimoto:“Q3DE: A fault-tolerant quantum computer architecture for multi-bit burst errors by cosmic rays,”the 55th IEEE/ACM MICRO, pp. 1110-1125,2022.

(7) Y.Ueno, M.Kondo, M.Tanaka, Y.Suzuki, and Y.Tabuchi:“QULATIS: A Quantum Error Correction Methodology toward Lattice Surgery,”2021 IEEE HPCA, pp. 274-287,2022.

(8) Y.Ueno, M.Kondo, M.Tanaka, Y.Suzuki, and Y.Tabuchi:“QECOOL: On-Line Quantum Error Correction with a Superconducting Decoder for Surface Code,”2021 58th ACM/IEEE DAC, pp. 451-456,2021.

(9) N.Yoshioka, T.Okubo, Y.Suzuki, Y.Koizumi, and W.Mizukami:“Hunting for quantum-classical crossover in condensed matter problems,”arxiv preprint arXiv:2210.14109,2022.

(10) Y.Suzuki, Y.Kawase, Y.Masumura, Y.Hiraga, M.Nakadai, J.Chen, K.M. Nakanishi, K.Mitarai, R.Imai, S.Tamiya, T.Yamamoto, T.Yan, T.Kawakubo, Y.O. Nakagawa, Y.Ibe, Y.Zhang, H.Yamashita, H.Yoshimura, A.Hayashi, and K.Fujii:“Qulacs: a fast and versatile quantum circuit simulator for research purpose,”Quantum,Vol.5, p.559,Oct.2021.

鈴木 泰成

量子計算をどのように抽象化し組み上げていくかはまだ標準的な考え方が確立していないフロンティアです。これまでの計算機を組み上げるうえでつくられてきたノウハウを集約し、高機能な量子コンピュータのあるべき姿を探求します。