2020年5月号

Focus on the News

超低遅延処理のための高性能な光論理ゲートを実現

NTTは、超低遅延処理のための高性能な光論理素子を実現しました。

電子演算回路は論理ゲートによって構成されますが、演算遅延(レイテンシ)の増大が消費電力と同様に問題となっています。本研究グループは、「光の干渉」だけで動作する小型な光論理ゲート“Ψ(プサイ)ゲート”の低損失かつ高速な動作に世界で初めて成功しました。この技術により、単一のΨゲートだけで代表的な論理演算(AND/XNOR/NORなど)が、超低遅延かつ波長無依存に実施できます。高速な光変調器との集積により、波長チャネルごとに独立した演算を割り当てること(波長分割演算)が可能になります。今後パタンマッチング処理や光ニューラルネットワークなど、特定の機能において従来にない超低遅延性を実現し得る、新たな光電子融合情報処理基盤の要素技術となることが期待されます。

本研究成果は、2020年3月6日に英国科学誌「Communications Physics」のオンライン版で公開されました。

なお、本研究の一部は、科学技術振興機構(JST) CREST「集積ナノフォトニクスによる超低レイテンシ光演算技術の研究」の支援を受けて行われました。

研究の背景

CMOS(相補型金属酸化膜半導体)電子回路技術による情報処理基盤は、主に作製技術の進化と集積密度の増大によって、これまで成長を維持してきました。しかし、電子回路の微細化によって、もれ電流や配線抵抗の増加が引き起こされることで、成長が頭打ちになりつつあります。これを受け、各科学技術分野で新しい情報処理基盤の探索が加速しています。さらに配線抵抗の増大は、電子回路の応答速度を制限するため、演算遅延(レイテンシ)はすでにどんどん悪化しています。このような演算遅延の限界を克服するため、「超低遅延なナノフォトニックプロセッサ」と「ハイエンドなデジタル電気信号処理」を融合させた、「超低遅延かつ超低消費電力な光電子融合アクセラレータ」の実現が期待されています。低遅延化の原理は、「光信号がプロセッサ内をほぼ光速で伝わること」に尽きますが、プロセッサ内の回路長をさらに短くする、つまり回路内の光ゲートの小型化が進むほど、さらなる低遅延化が見込めます。

本研究グループでは、これまでに培ってきたナノフォトニクス技術を駆使することで、上記のナノフォトニックプロセッサの要素技術である「ナノ受光器」「ナノ光変調器」、またこれらの高度な組み合わせである「光トランジスタ」を実現してきました。しかしながら、「光トランジスタ」だけで光の低遅延性を損なわずに演算回路を組むことは容易ではなく、実際にはさまざまな要素を協調させることで、初めて具体的な機能を持つ低遅延かつ低消費電力なナノフォトニックプロセッサが実現できます。特に光の低遅延性に的を絞った光ゲートについてはこれまで未検討でした。

研究の成果

本研究グループは、上記のシリコンフォトニクス技術を前提とした素子構造を探索することで、3µm長の低損失かつシンプルなシリコン細線 Ψゲートを見出し、これによる低損失・高速・波長無依存な論理演算動作を世界で初めて実験実証しました。本成果のポイントを次に説明します。

(1) シリコン細線Ψゲートによる低損失かつ高速な光論理演算の実現

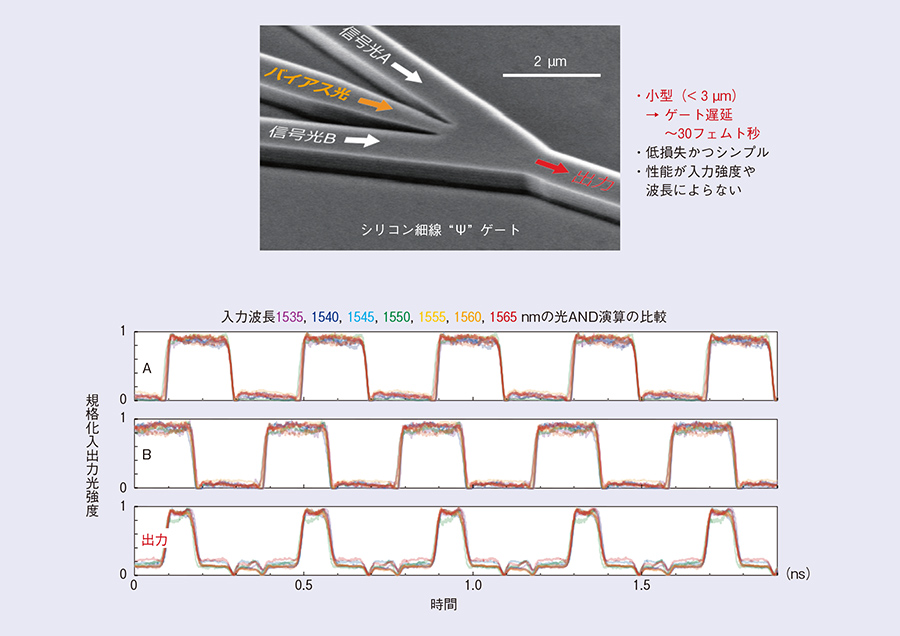

光波シミュレーションによって最適化されたシリコン細線Ψゲートを作製し、20 Gbit/sの高速なランダム光信号ビット列A、B、およびバイアス光の3つを同時入力する実験を実施しました(図上)。その結果、適切な振幅のバイアス光を入力することで2階調の明瞭なAND動作が観測されました(図下)。このようなオンチップの微小な素子において光の干渉を用いた高速かつ明瞭なAND動作の観測は世界初で、シリコン細線Ψゲートの低損失性がもたらした結果です。光AND演算に要する演算遅延はおよそ30フェムト秒であることが素子長から推測されます。電子回路でのゲート遅延は10ピコ秒程度であることが知られるため、極めて低遅延です。

(2) 単一素子における光論理演算機能の切り替え動作の実現

上記と同じ素子に対して、各位相関係を保ちつつバイアス光の入力強度を適切に増大したところ、光XNOR動作および光NOR動作への動作の切り替えに成功しました。光AND動作同様、これらの高速な光論理演算の動作の観測も世界初です。

(3) 入力波長に無依存な光論理演算動作の実現

上記と同じ素子に対して、入力光の波長を1535から1565 nmまで5nmずつ変更し、計7波長それぞれに対する光AND動作の結果を重ね合わせたところ、ほぼ波長無依存な動作が可能であることを確認しました(図下)。このような明瞭な光AND動作での確認例は本成果が初です。異なる波長を同時に入力したとしても、波長間で相互作用はほとんどありませんので、最終的には「波長チャネルごとに異なるビット列と異なる論理演算を割り当てたうえで、独立した演算を単一のゲートで同時に実行できる機能」(波長分割演算)が可能になることが期待されます。これは非線形光学ゲートを用いた場合では実現が極めて困難な動作の1つです。

図 シリコン細線Ψゲートによる高速かつ波長無依存な光AND演算動作の実証

今後の展開

シリコン細線Ψゲートは、従来では成し得なかった小型化(低遅延化)と低損失化のトレードオフを打破する光論理素子として世界初で、従来の電子回路技術のみでは悪化する一方であった演算遅延を、光演算技術を組み合わせることで抜本的に解決できる可能性を示すものです。今後、パタンマッチングやベクトル(積和)演算といった応用で光電子融合アクセラレータの要素技術となることが期待されます。

問い合わせ先

NTT先端技術総合研究所

広報担当

TEL 046-240-5157

E-mail science_coretech-pr-ml@hco.ntt.co.jp

URL https://www.ntt.co.jp/news2020/2003/200306a.html

研究者紹介

技術転換期において、光をいかにうまく「演算」に使うか

北 翔太

NTT物性科学基礎研究所

研究主任

「光演算」という研究テーマは、今話題の「ニューラルネットワーク」と同じく、1980年代に最初のピークを迎えた古いものです。当初最大の利点として主張していた「空間並列処理能力」が、電子回路の圧倒的な集積度に敗北した経緯があります。しかし時は過ぎ、電子回路技術の進化はほぼ物理的な限界に達してしまいました。その一方で、光回路技術は今まさに成熟期を迎え、いくつかの重要な光素子がチップ上に高信頼に集積できるようになり、チップ上の光ネットワークのスケールや機能がこの数年で劇的に進化してきました(ムーア則黎明期の光版?)。このような技術転換期を背景に、「光演算の魅力をもう一度考え直してみよう」というのが本研究のスタートラインであり、おそらく今後も継続していくスタンスです。

本研究について現状で私が認識していることは、おそらく現在の電子回路の仕組みに光素子を無理矢理当てはめて、パーツを置き換えようとしても、それは「おにぎりを味噌汁でつくる」ように突飛で効率が悪いことだろう、ということです。ここはぜひ「おにぎりをより美味しく味わうために究極の味噌汁をつくる」(光電子融合)というもっと自然な方向性で、今後も研究に取り組んでいく所存です。そのうえで光の強みを全面に押し出した(なおかつ弱点を隠蔽した)新たな演算器のコンセプトを世界に先駆けて実証し、IOWNの重点課題の1つである「情報処理基盤」の創成の一助を担えれば幸いです。