2021年3月号

特集

新原理コンピュータへの取り組み

- 量子コンピュータ

- 量子アニーリング

- コヒーレントイジングマシン

現代のコンピュータとは異なる原理で動作する、量子コンピュータやイジングマシンなど非ノイマン型のコンピュータが注目を集めています。組合せ最適化問題、量子化学計算、素因数分解など特定の問題において威力を発揮しますが、どれも社会にインパクトのある重要な問題であるため、精力的に研究が進められています。本特集では、新原理コンピュータの進展を解説しながら、NTT研究所における理論と実験に関する取り組みを紹介します。

齊藤 志郎(さいとう しろう)†1/後藤 秀樹(ごとう ひでき)†2

NTT物性科学基礎研究所†1

NTT物性科学基礎研究所 所長†2

新原理コンピュータ

現在の半導体業界には「集積回路上のトランジスタの数が18カ月ごとに倍になる」というムーアの法則と呼ばれる経験則が存在します。実際に半導体素子はこの法則に従い微細化が進み、コンピュータの性能は年々向上しています。この経験則が今までどおり実現されていくと、トランジスタのサイズが微小化し、原子サイズで限界を迎えます。しかし、その前に量子効果が現れ従来の電気回路の法則が成り立たなくなる「量子力学の壁」があるといわれています。量子力学の世界には、重ね合わせ状態、粒子と波動の二重性など古典力学ではみられない不思議な性質があります。これらの性質を積極的に利用し従来とは異なる原理で動作するコンピュータが量子コンピュータです。現在の情報処理では、“0”と“1”の2値を取り得るビットを用いて計算が進みますが、量子コンピュータの基本素子である量子ビットは“0”と“1”の任意の重ね合わせ状態を実現できます。量子ビットをN個準備すると、2N個の状態の重ね合わせを表現することができ、量子ビットの数を増やすと重ね合わせの状態数が指数関数的に増えます。この膨大な数の重ね合わせ状態に対して演算を進めることで超並列計算が可能となり、量子コンピュータの速さの要因となっています。また、量子コンピュータでは量子ビットの波としての性質を利用し、量子ビット間の位相の干渉効果により、超並列計算の結果から所望の解を見つけ出します。従来の逐次計算に基づくノイマン型のコンピュータとは異なり、量子コンピュータのように、新しい原理で動作する非ノイマン型のコンピュータが近年注目を集めています。本特集では、NTT研究所における新原理コンピュータに関する取り組みを、理論と実験の両面から紹介します。

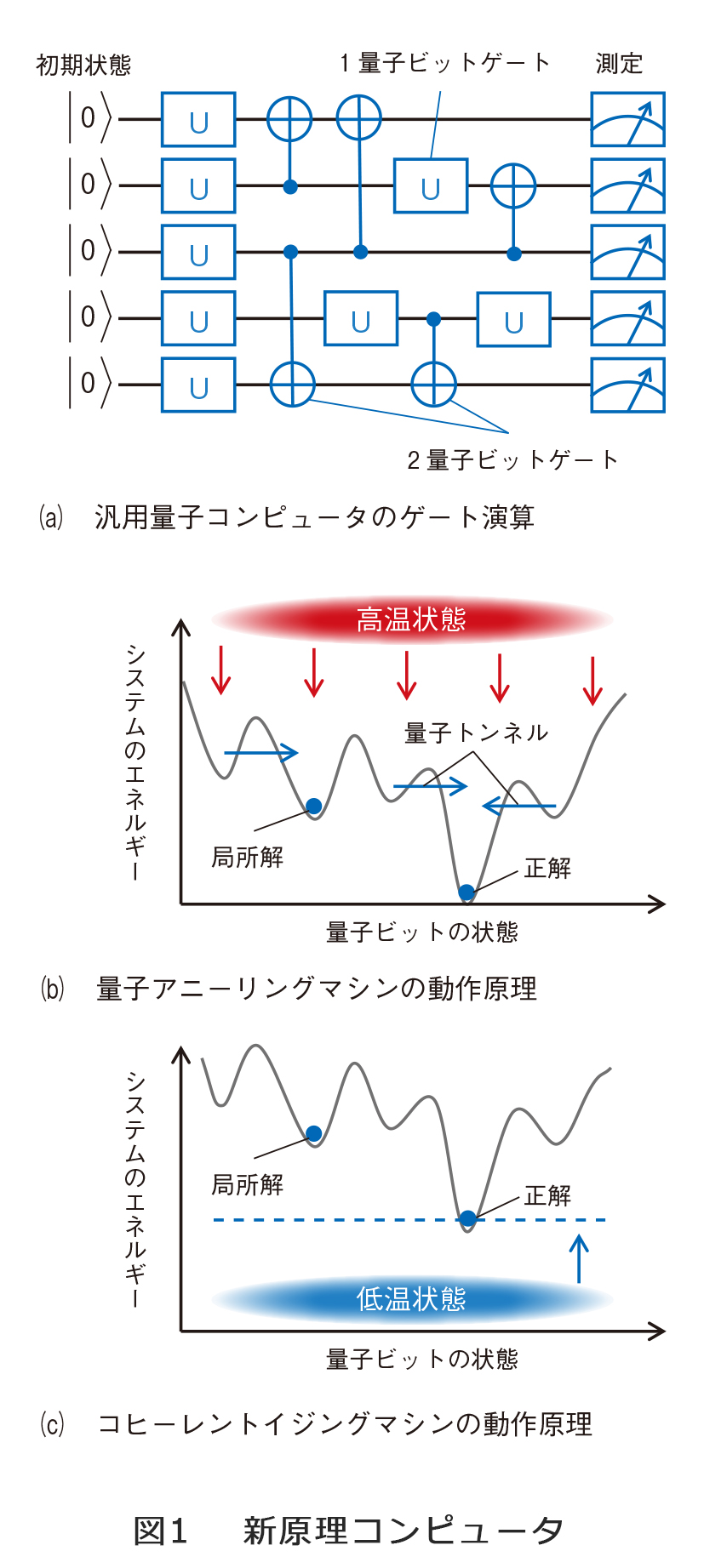

新原理コンピュータは大きく分けて2つのタイプ、すなわち汎用量子コンピュータと量子アニーリングマシンに分けられます。前者は、多数の量子ビットを基底状態に準備し、図1(a)に示すように1量子ビットゲート操作と2量子ビットゲート操作を繰り返しながら計算を進めます。因数分解や大規模検索に関する量子アルゴリズムが発見されており、古典アルゴリズムよりも高速化されることが理論的に証明されています。しかし、量子ビットは外部ノイズに弱く、エラーが頻繁に発生するため、量子誤り訂正用の冗長な量子ビット、すなわち膨大な数の量子ビットが必要となります。例えば、2048ビットの数を因数分解するために2千万個の量子ビットが必要という試算があります(1)。この規模の量子ビットを現在の技術で作製することは非常に困難です。後者は、図1(b)に示すように、多数の量子ビットをすべての状態の重ね合わせ、すなわち高温状態に準備し、徐々に冷却することでエネルギー最低状態(正解)を見つけ出します。途中、局所的な安定点からは量子的なトンネル効果で抜け出すことができるため、古典的なアニーリングアルゴリズムよりも速く正解に到達するといわれています。量子性による高速化は厳密には証明されていませんが、社会的ニーズの高い組合せ最適化問題の近似解が得られるため、注目を集めています。また、安定な状態をゆっくりと変化させながら計算が進むため外部ノイズに強いという特徴もあります。このタイプのコンピュータでは、最適化問題を物理系に実装する際に、イジングモデルと呼ばれる相互作用するスピン系を表す物理モデルが使われるため、イジングマシンとも呼ばれています。

イジングマシン

超伝導量子ビットを用いた汎用量子コンピュータの研究において、2量子ビットゲート操作を実証、3量子ビットのもつれ状態を観測といった成果が報告されていた2011年に、カナダのベンチャー企業D-Wave Systemsから衝撃的なニュースが発表されました。128量子ビットを実装した量子アニーリングマシン(D-Wave One)が世界初の商用量子コンピュータとして発表されたのです。これは、超伝導量子ビットを用いて計算するイジングマシンです。超伝導ニオブを用いたD-Wave Oneの量子ビットは、汎用量子コンピュータで用いられるアルミニウム製の量子ビットと比較して、圧倒的に量子情報のメモリ時間が短いため、当時、量子性を疑う研究者もいましたが、その後の実証実験で量子性による高速化が確認されています。2013年には512量子ビットのD-Wave Two、2015年には1000量子ビット超のD-Wave 2X、2017年には2048量子ビットのD-Wave 2000Q、2020年には5000量子ビット超のD-wave advantageを発表しており、世界中の企業が同社の提供するクラウドサービスを利用し、量子イジングマシンのビジネス利用に関する研究開発を進めています。しかし、実際のビジネス応用にはさらなる大規模化が必要となります。さらに、超伝導量子ビットはチップ上の固体素子であるために、量子ビット間の結合が近接量子ビット間に限られるという制約があります。そのため、最適化問題を量子アニーリングマシンに実装する際には、問題のサイズよりも多くの量子ビットが必要になります。

一方、NTT研究所では、縮退光パラメトリック発振器(DOPO)を人工スピンとして用い、多数のDOPOパルスを光ファイバ共振器中に閉じ込めることにより、スピン間の全結合を実装可能なコヒーレントイジングマシン(CIM)を開発しました。ファイバ共振器の全長を延ばすことで、人工スピンの数を増やすことが可能なため、固体素子と比べて、大規模化が比較的容易であると考えられます。CIMでは、DOPOの励起光の強度を徐々に強めることにより、図1(c)に示すように低温側から解を探索し、系のエネルギーが最適解に到達した時点で、正解がみつかります。DOPOの量子的性質が計算機としての性能にどう寄与しているかはまだ研究途上ですが、MaxCut問題と呼ばれる典型的な組合せ最適化問題において、古典アニーリングアルゴリズムと比較して、高速化が実証されています(2)。本特集記事『コヒーレントイジングマシンと量子アニーリングの性能比較実験』(3)では、コヒーレントイジングマシンとD-Wave Systems社の量子アニーリングマシンの比較実験を紹介します。

汎用量子コンピュータ

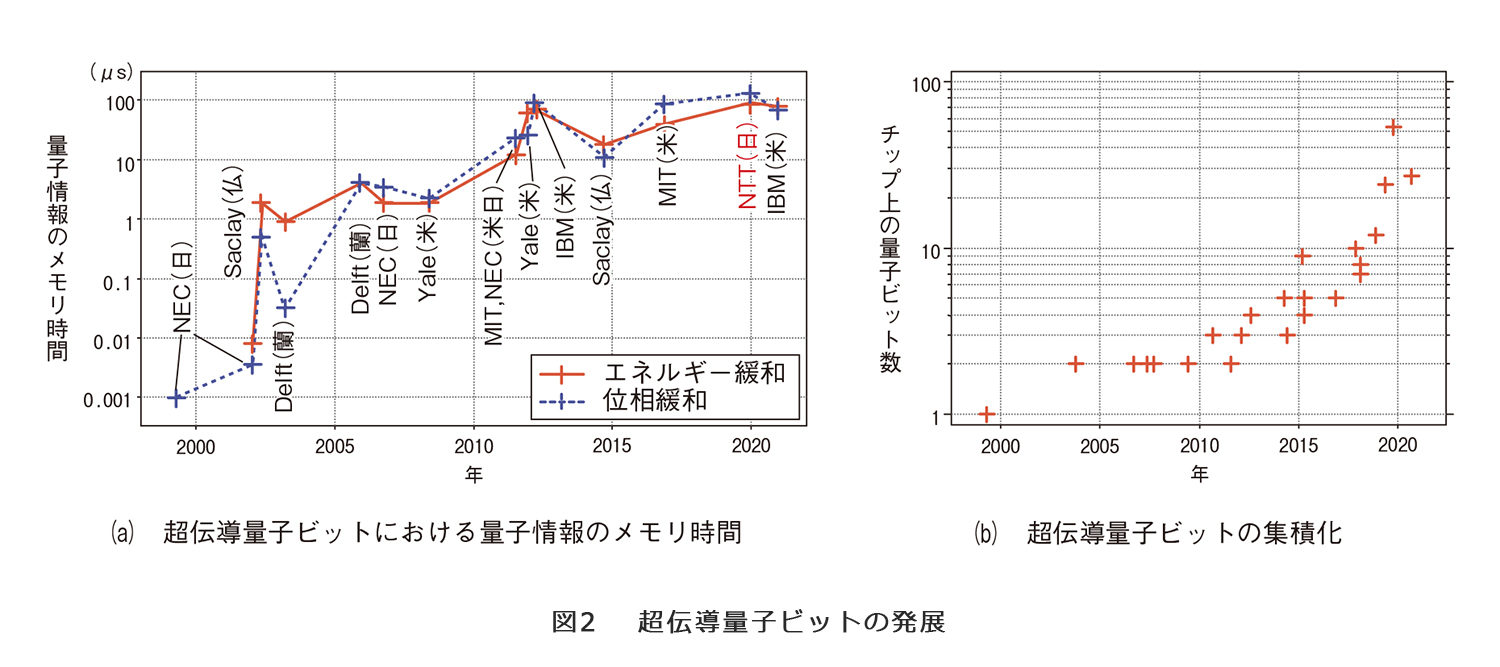

今から20年ほど前は、量子コンピュータの基本素子である量子ビットをいかに実現するかが問題となっていました。量子ビットには“0”と“1”の重ね合わせ状態を実現するための量子2準位系が必要ですが、どのような物理系を用いるべきか議論されていました。量子情報のメモリ時間の長い原子や電子は有望だが集積化が難しい、逆にメモリ時間は短いが半導体や超伝導量子ビットは固体素子であるために半導体集積化技術が使える、光量子ビットは光通信との相性が良いなど、さまざまな候補が検討されました。実は、この議論は現在も続いており、それぞれの物理系がそれぞれの特徴を活かして発展してきました。超伝導量子コンピュータは50~70量子ビット、イオントラップ量子コンピュータは32量子ビット、半導体ドット量子コンピュータは2~3量子ビットの集積度を達成しています。特に、2019年にGoogleから発表された、53量子ビットを有する超伝導量子コンピュータが従来のスーパーコンピュータを上回ったとする「量子優位性の実証」は大きな話題となりました(4)。量子コンピュータが得意とする問題を解かせた結果で、すべての問題において量子コンピュータが優れていることを実証したわけではありませんが、非常に重要なマイルストーンを達成したといえます。このマイルストーン達成に向けた超伝導量子ビットの発展を図2に示します。1999年に初めて超伝導量子ビットが動作したときはメモリ時間が1 nsと短く、非常に難しい実験でしたが、2012年ごろには約100 μsまで延びて5桁も改善しました。その後、メモリ時間はそれほど延びていませんが、チップ上の量子ビット数が急激に増えています。これは、同時期に集積化に向けて最低限必要なメモリ時間が達成されたため、多くの研究機関で研究の方向性がメモリ時間延長から集積化へシフトしたためと考えられます。こうして、現在ではGoogle、IBM、Intelが50量子ビットの超伝導量子コンピュータチップを開発し、量子優位性が示されるまでに発展しました。

NTT研究所では、現在の超伝導量子コンピュータチップに集積化されている量子ビットとは異なるタイプの超伝導量子ビットの研究を続けてきました。その特性を活かして、巨視的量子重ね合わせ状態の検証(5)といった基礎物理の研究から、局所的な高感度磁場センサへの応用(6)まで、さまざまな取り組みを行ってきました。本特集記事『ボソニック量子計算に向けた長寿命周波数可変量子ビット』(7)では、NTTの超伝導量子ビットが世界最高レベルのメモリ時間を記録した成果(図2(a))と、量子コンピュータへの応用の可能性を紹介します。

誤り耐性量子コンピュータに向けて

量子優位性が示されたというニュースを聞くと、実用的な量子コンピュータがもうすぐ実現されるのではと思われるかもしれませんが、実は道のりは長いといわざるを得ません。現状の汎用量子コンピュータは集積度が50量子ビット程度です。さらにノイズの影響で量子情報が時間とともに失われ、ゲート操作が誤りを伴うため、何回もゲート操作を繰り返すような複雑な計算を実行することができません。このように機能や規模において制約のある量子コンピュータはNISQ(Noisy Intermediate-Scale Quantum)デバイスと呼ばれています。NISQデバイスでも量子優位性を示すことから、量子のポテンシャルをうかがい知ることができますが、実用に堪え得る大規模で複雑な量子計算を実行するためには誤り耐性量子コンピュータが必要となります。そのためには、複数の量子ビット(物理量子ビット)を準備し冗長性を持たせることで、誤り訂正可能なノイズに強い1つの量子ビット(論理量子ビット)を構成します。さらに、物理量子ビットを制御するレイヤ、論理量子ビットを制御するレイヤ、その上位のアルゴリズムを実行するレイヤなど複雑なレイヤ構造が必要となります。本特集記事『量子コンピュータの設計に向けて』(8)では、誤り耐性量子コンピュータがどのようなレイヤ構造を持つシステムとなるべきかを理論的に検討した結果を紹介します。より具体的には、論理量子ビットを構築するためには、多数の物理量子ビットを集積化するだけではなく、ソフトウェアの開発も必要です。例えば、個々の物理量子ビットの特性を評価したのち、制御系を効率良く校正するプログラムが必要です。さらに、誤り訂正のための演算やフィードバック回路を設計します。この設計を評価するためには量子回路シミュレータが必須です。本特集記事『量子情報処理の誤り耐性技術とその実装方式』(9)では、このような誤り耐性量子計算に向けたソフトウェア基盤の研究開発を紹介します。

冒頭でも述べたように、誤り耐性量子コンピュータには、2千万個の物理量子ビットが必要といわれています。そのための量子ビット集積化技術や制御技術は日進月歩で進化していますが、まだまだブレイクスルーが必要です。近い将来の目標としては、誤り訂正をしないNISQデバイスを高性能化し、従来型コンピュータとハイブリッド化することで、量子機械学習や量子化学計算への応用が検討されています。NTT研究所では、計算理論や情報理論の知見に基づいて、NISQデバイスの能力を最大限利用するための研究を進めています。本特集記事『量子コンピュータの実装技術の課題克服に向けた理論面からの取り組み』(10)では、操作可能な手段を制限することでノイズを除去する、あるいは初期化されていない量子ビットを高速アルゴリズムで有効活用するなど、NISQデバイス*の性能を向上する方法を紹介します。さらに『量子情報処理の誤り耐性技術とその実装方式』(9)では、NISQデバイスのノイズを補償する手法として、計算コストは増えるが量子ビット数を増やす必要のない量子誤り抑制について解説します。

*ここでの「NISQデバイス」とは、誤り訂正機能を備えたフルスペックの量子コンピュータが完成するまでに得られる、機能に制約のある量子コンピュータ全般を広く意味しており、本記事で紹介する技術は、必ずしも近い将来に使用可能であるわけではありません。

今後の展開

20年前は、1量子ビットを実装するための研究が行われ、量子コンピュータは100年先の技術ともいわれていました。10年前は、2量子ビットゲートが実現し、どのように量子ビットの数を増やしていくかが研究対象となり、量子コンピュータは50年後には実現の可能性があるという声が聞かれるようになりました。現在は、数十ビットの量子コンピュータが動作し、量子優位性が示されています。さらに数千ビットを有するイジングマシンが実現され、一部商用化されています。国のプロジェクトでは、30年後の誤り耐性量子コンピュータの実現が目標に掲げられるようになりました。このように新原理コンピュータに関しては加速度的に研究が進み、研究者も増え、裾野が広がっていると思います。とはいえ、道のりが長いことも確かです。実験研究者にとっては、大規模化に向けたブレイクスルーが必須です。現代のLSI(大規模集積回路)のようにイールドの高いプロセス技術、制御系も含めた集積化技術、あるいは、分散量子コンピューティングに向けたネットワーク技術が必要になるかもしれません。理論研究者にとっては、リソースのかからない量子誤り訂正符号や新しい量子アルゴリズムなどのブレイクスルーが期待されます。あるいは、非凡な科学者が全く新しいアイデアを提案し、問題解決が一気に進むかもしれません。いずれにせよ、何が起こるか分からない挑戦的なテーマであることは確かであり、今後も、この分野の発展を注視していきたいと思います。

■参考文献

(1) C. Gidney and M. Ekera: “How to factor 2048 bit RSA integers in 8 hours using 20 million noisy qubits,”arXiv:1905.09749,2019.

(2) 武居・稲垣・稲葉・本庄:“複雑な組合せ最適化問題を解く量子ニューラルネットワーク,”NTT技術ジャーナル,Vol. 29,No. 5, pp. 11-14,2017.

(3) 武居・稲垣・稲葉・本庄:“コヒーレントイジングマシンと量子アニーリングの性能比較実験,”NTT技術ジャーナル,Vol. 33,No. 3, pp. 18-22,2021.

(4) F.Arute,K.Arya,R.Babbush,D.Bacon,J.C.Bardin,R.Barends,R.Biswas,S.Boixo,F.G. S. L. Brandao,D.A. Buell,B.Burkett,Y.Chen,Z.Chen,B.Chiaro,R.Collins,W.Courtney,A.Dunsworth,E.Farhi,B.Foxen,A.Fowler,C.Gidney,M.Giustina,R.Graff,K.Guerin,S.Habegger,M.P. Harrigan,M.J. Hartmann,A.Ho,M.Hoffmann,T.Huang,T.S. Humble,S.V. Isakov,E.Jeffrey,Z.Jiang,D.Kafri,K.Kechedzhi,J.Kelly,P.V. Klimov,S.Knysh,A.Korotkov,F.Kostritsa,D.Landhuis,M.Lindmark,E.Lucero,D.Lyakh,S.Mandrà,J.R.McClean,M.McEwen,A.Megrant,X.Mi,K.Michielsen,M.Mohseni,J.Mutus,O.Naaman,M.Neeley,C.Neill,M.Yuezhen Niu,E.Ostby,A.Petukhov,J.C.Platt,C.Quintana,E.G.Rieffel,P.Roushan,N.C.Rubin,D.Sank,K.J.Satzinger,V.Smelyanskiy,K.J.Sung,M.D.Trevithick,A.Vainsencher,B.Villalonga,T.White,Z.J.Yao,P.Yeh,A.Zalcman,H.Neven,and J.M.Martinis:“Quantum supremacy using a programmable superconducting processor,”Nature,Vol.574,pp.505-510,Oct.2019.

(5) 角柳・松崎・樋田・山口・齊藤・Munro:“巨視的スケールでの実在性の破れを実証,”NTT技術ジャーナル,Vol. 29,No. 5, pp. 20-23,2017.

(6) Focus on the News:“超伝導量子ビットによる高感度・高空間分解能電子スピン共鳴に成功,”NTT技術ジャーナル,Vol. 31,No. 8, pp. 71-72,2019.

(7) Abdurakhimov・Mahboob・樋田・角柳・齊藤:“ボソニック量子計算に向けた長寿命周波数可変量子ビット,”NTT技術ジャーナル,Vol. 33,No. 3, pp. 23-29,2021.

(8) Munro・Bastidas・東・根本:“量子コンピュータの設計に向けて,”NTT技術ジャーナル,Vol. 33,No. 3, pp. 30-36,2021.

(9) 徳永・鈴木・遠藤・浅岡:“量子情報処理の誤り耐性技術とその実装方式,”NTT技術ジャーナル,Vol. 33,No. 3, pp. 43-48,2021.

(10) 秋笛・竹内・高橋・加藤・谷:“量子コンピュータの実装技術の課題克服に向けた理論面からの取り組み,”NTT技術ジャーナル,Vol. 33,No. 3, pp. 37-42,2021.

(左から)齊藤 志郎/後藤 秀樹

研究の初期段階では、理論と実験が理想と現実の両極から攻めますが、新原理コンピュータの研究は両者の距離が近づいてきていると思われます。NTT研究所の所を横断したコラボレーションが進むことを期待しています。