2021年5月号

特集

ディスアグリゲーテッドコンピューティングのための光電融合技術

- IOWN

- ディスアグリゲーテッドコンピューティング

- 光電融合

NTTでは、ディスアグリゲーテッドコンピューティングを実現するための光電融合技術について検討を行っています。本稿では、光電融合技術のコンセプトについて説明し、ディスアグリゲーテッドコンピューティングに光を導入することがなぜ有効なのかを示し、さらに検討中の低消費電力デバイスについて紹介します。

坂本 健(さかもと たけし)/佐藤 昇男(さとう のりお)

瀬川 徹(せがわ とおる)

NTT先端集積デバイス研究所

IOWNのコンピューティングを支える光電融合技術

本特集記事『IOWNを支えるディスアグリゲーテッドコンピューティング』(1)で説明したように、IOWN(Innovative Optical and Wireless Network)の実現のためには、これまでと比較にならない大量のデータを効率良く処理できるコンピュータが必要となります。この大量のデータを効率良く処理する画期的なコンピュータを支える重要な技術が、光電融合技術です。

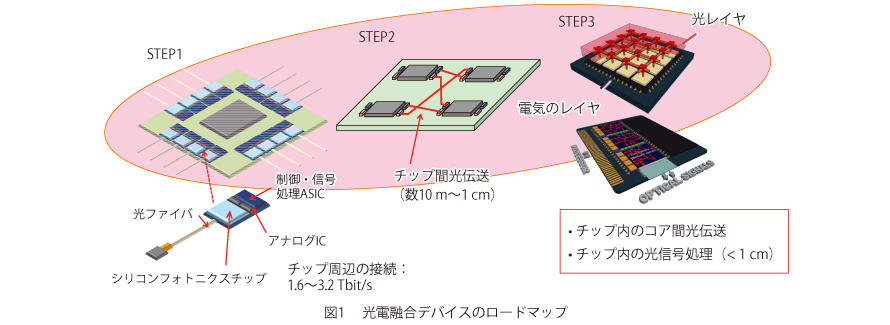

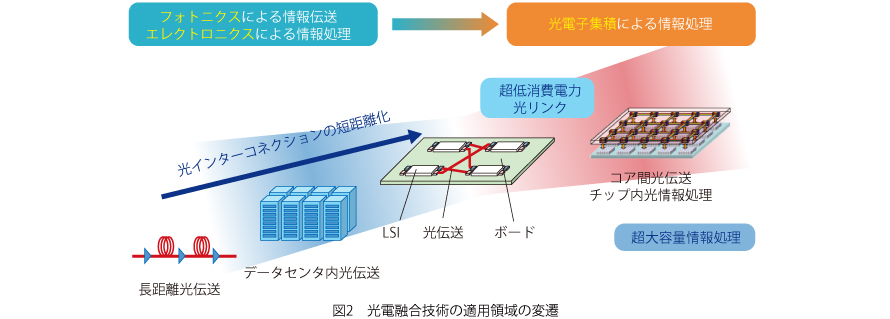

光電融合デバイスのロードマップを図1に示します(2)。シリコンフォトニクス技術を利用したコンパクトな光モジュールを中央のLSI(大規模集積回路)の周囲に配置する形態のSTEP1から始まり、LSIの直近にレーザや光受信器等の光伝送用素子が配置されるSTEP2、そして LSIチップ内も光配線で接続するSTEP3と、世代が進むごとに小型化・短距離化が進んでいきます。STEP1ではコンピュータ間をつなぐ通信をターゲットとして開発が始まりますが、STEP2、STEP3と進化するにつれ適用領域が装置内・ボード内インターコネクトへ移り、コンピュータ内部への光の導入が進んでいくと考えられています(図2)。

ディスアグリゲーテッドコンピュータで考えているラックスケールのコンピュータ内接続では、数mを超える伝送距離が必要となります。これを電気接続で実現しようとした場合、高速化・長距離化のために爆発的な電力増加が伴い、実現は困難です。STEP2やSTEP3の高速・高密度・低消費電力の光電融合デバイスによりLSI直近で電気を光に変換することで、電気伝送の限界に縛られることなく、高い処理性能を持つコンピュータをより低い消費電力で実現できます。

本稿では、ディスアグリゲーテッドコンピュータの低消費電力を実現するための光電融合デバイス技術について詳しく説明します。

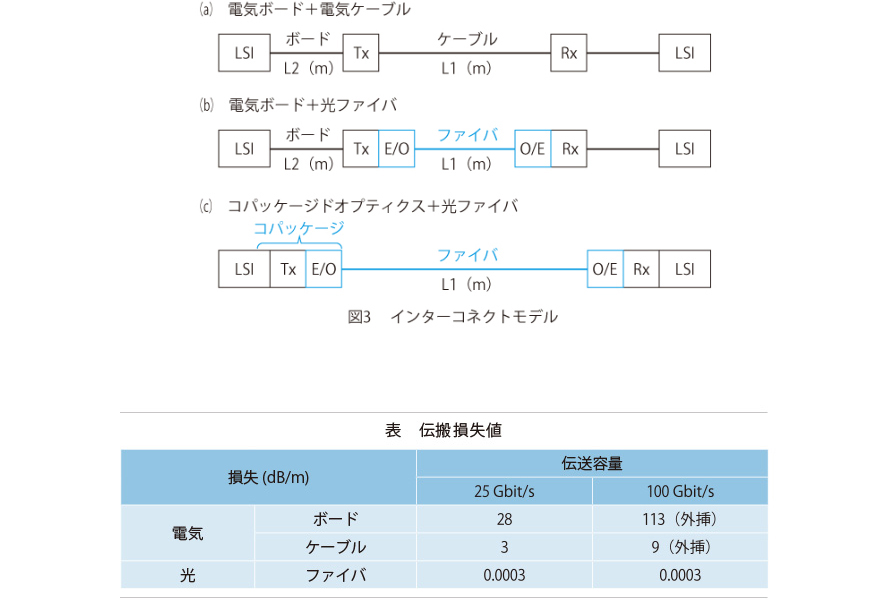

光インターコネクトの必要性

装置内のボード間接続、そしてボード内のLSI間接続に、電気ではなく光を使う必要性についてインターコネクトモデルを用いて説明します。図3(a)はすべて電気のモデルで、LSIがボード上に搭載され、LSIのクロック周波数から変換された高速信号がボード上の電気配線を通して途中の送信器(Transmitter: Tx)につながります。その後、同軸ケーブルを経由してボードに形成された受信器(Receiver: Rx)で受信されてLSIに送られます。このとき、ボード間をつなぐケーブルの長さをL1 (m)、1つのボード上での配線長をL2 (m) とします。図3(b)は、送信器の後に電気-光変換器(Electrical-to-optical converter: E/O)を配置して光信号にし、同軸ケーブルの代わりに光ファイバを用いた場合です。図3(c)は、送信器と電気-光変換器をLSIの近傍で同一パッケージ内に集積した場合で、この形態はコパッケージドオプティクス(Co-Packaged Optics: CPO)と呼ばれ図1および図2に対応します。

ボード(プリント基板)、同軸ケーブル、光ファイバを高速信号が伝搬するときの単位長さ当りの損失値を表に示します。25 Gbit/sの信号については製品の値を参照しています。ボードや同軸ケーブルは光ファイバに比べて伝搬損失が大きいことが分かります。例えば、同軸ケーブルで3 dB/mというのは、信号が1 m伝搬する間に、大きさが−3 dB、すなわち半分になるということです。100 Gbit/sの信号については測定が難しいので、一部外挿した値を示しています。現在は1チャネル当り25 Gbit/s(12.5 GHz)程度の信号を基に各種多値化の技術が用いられていますが、将来的にもCMOSテクノロジの速度の限界は100 Gbit/s程度と考えられます。信号が高速になるほど電気での損失は増加することが分かります。

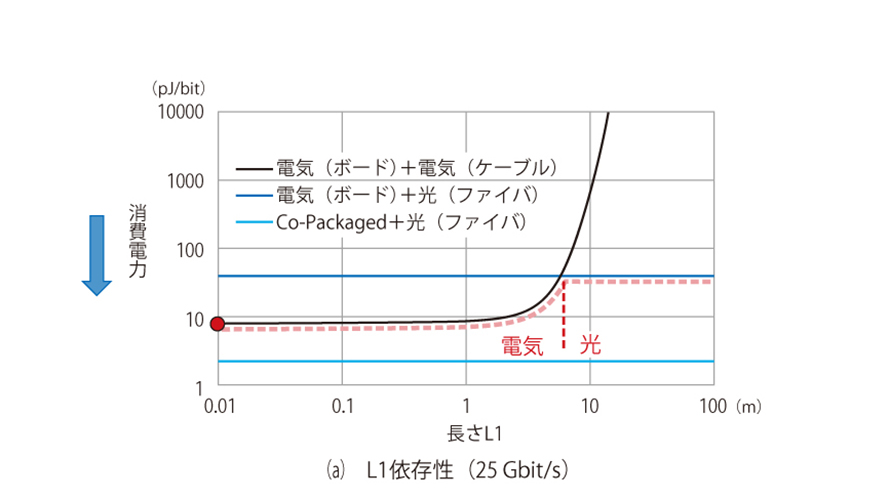

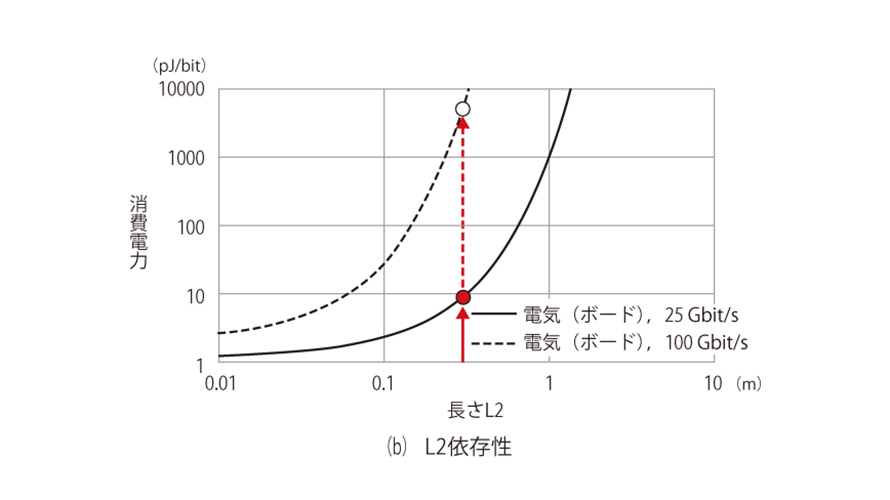

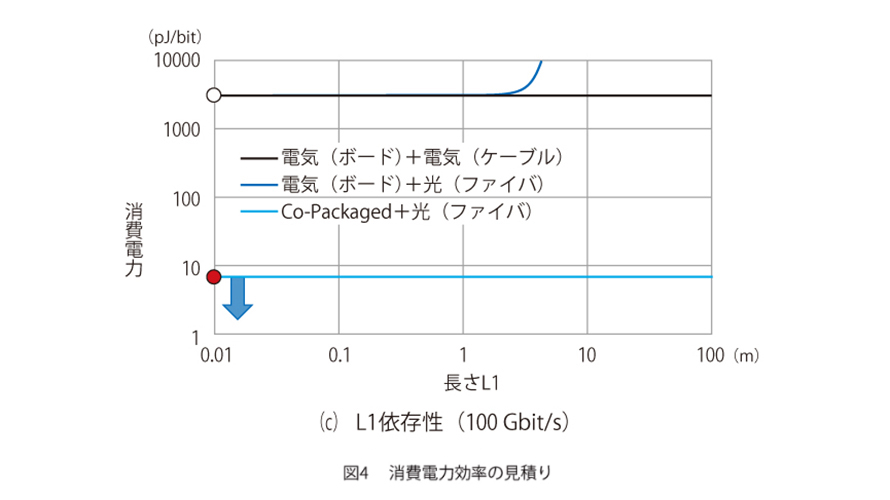

これらを用いて、消費電力と距離の関係を見積もった結果を図4に示します。図4(a)の縦軸は、消費電力(mW)を伝送容量(Gbit/s)で割った値(mW/Gbit/s = pJ/bit)を指標にとり、値が小さいほど効率が良いことを示します。横軸は、ボード間の距離 L1 (m) としました。このときに現在製品化されている25 Gbit/s×4チャネルのプラガブルトランシーバを参考に計算した結果を示します。電気の場合と、光ファイバを用いた場合を比較すると、5mを境に電気が有利な領域と光ファイバが有利な領域に分かれることが分かります。一方で、電気の場合でも下限(赤丸)があることが分かります。図4(b)にはボード上の配線長さL2 (m)と消費電力の関係を示します。25 Gbit/sの曲線でL2 = 0.3 mを伝送させるのに必要な消費電力で決まっていることが分かります。そこで、L2を極力小さくするようなコパッケージドオプティクスを使用すると、図4(a)に示した線(空色)のように、さらに効率を上げることができます。次に、将来的に伝送容量が増えて高速化された100 Gbit/sの場合を想定した結果を考えます。図4(b)の100 Gbit/sの点線に示すようにボードでの損失が桁違いに大きくなり、ボードが使えなくなることは自明です。仮に25 Gbit/sと同様の試算をしたものを図4(c)に示します。将来的には、可能な限りLSI直近で光・電気変換をするほど、それだけ消費電力を下げられることが分かります。さらに、25 Gbit/sに比べて100 Gbit/sにすると周波数が4倍になるため消費電力も増えています。高速化しながら低消費電力にする光電融合デバイスが必要になってきます。

インターコネクトの製品・研究開発動向

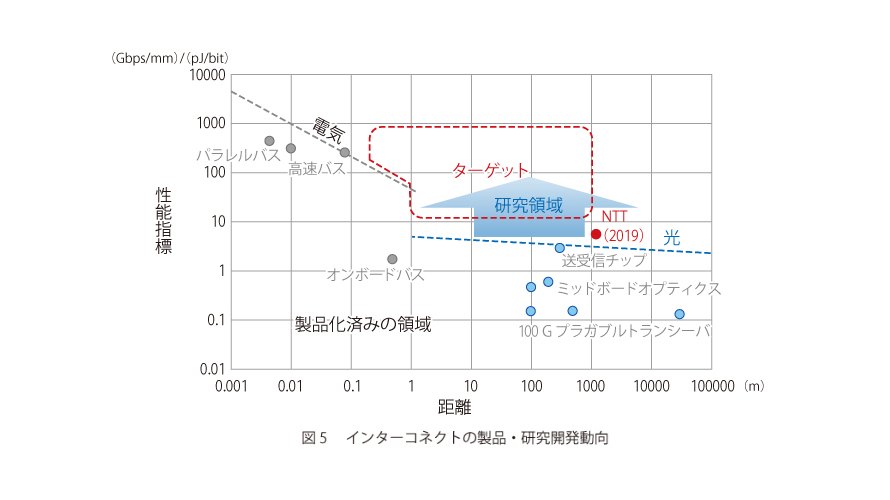

距離や速度に応じて光と電気の適用領域が変わってくることをモデルで示しましたが、ここでは製品や研究開発の動向について説明します。モデルでは単チャネルの場合を説明しましたが、実際はLSIの辺から複数チャネルを束ねて出して使用します。LSIの単位辺長さ(mm)から何Gbit/sの伝送容量が送受信できるかという辺密度(Gbit/s/mm)は高いほど良く、また単位伝送量当りの消費電力(pJ/bit)は低いほど良いので、前者を後者で割った値、高密度/低消費電力= (Gbit/s/mm)/(pJ/bit)を性能指標とします。この性能指標を図5の縦軸に、距離(m)を横軸にとっています。製品化済みのインターコネクトの値をプロットすると、光は長距離で適用されているものの、性能指標は電気に比べて2桁程度低い状況となっています。この性能指標を向上させる目的で、複数の研究開発機関から低消費電力・高密度の光送受信器がさかんに提案されています。100 m程度の長距離で使える光技術は10 cm程度の領域にも適用され、ボード上の電気の領域を光に置き換えていくことが期待されます。ディスアグリゲーテッドコンピューティングでは、さらに物理サーバサイズに閉じ込められていたLSIやメモリなどの間のデータ通信を、ラック間スケール(数10 m)まで拡大することになります。さらに、信号速度の高速化が必要になると電気配線では性能指数の劣化が予測されるため、数cmから数10 mの領域を光を用いて電気と同等レベルの性能指標で実現することがターゲットとなります。

NTTにおける低消費電力・高密度のデバイス研究開発

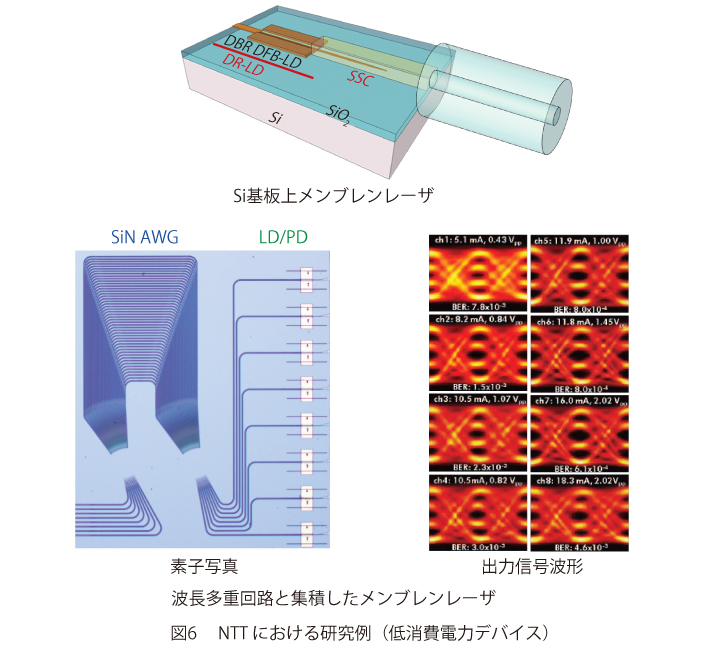

NTTでは、前述したターゲット領域に向けた低消費電力・高密度な光送受信器の研究開発を進めています。これまでの到達レベル(送信器チップ)について図5にプロットしました(3)。特に、光送受信器の中でも電気信号を光信号に変換する半導体レーザは重要な光デバイスです。NTTで作製した薄膜(メンブレン)レーザを図6に示します。ボード間伝送といった短距離光通信で現在もっともよく用いられる半導体レーザに面発光レーザ(VCSEL)が挙げられます。低消費電力で動作可能、低コストという特徴があるものの、その形状から波長多重(WDM)技術の適用に向きません。通信容量の増大には、単一モードで発振するレーザと、高密度集積可能な波長多重回路の集積が求められます。このような背景からNTTでは、短距離光インターコネクト用の光源としてSi基板上に作製したメンブレン直接変調レーザを開発しています。Si基板上にレーザを作製することで、波長多重回路や受光素子といった光デバイスを高密度かつ低コストに作製可能なSiフォトニクスの技術が適用できます。さらに、屈折率の低いSiO2層の上にLDを形成することで、光と注入キャリアとの高い相互作用により、レーザの小型化と低消費電力化を実現できます。現在までに、VCSELに匹敵するレーザ単体としての消費エネルギー200 fJ/bitでの25。8 Gbit/s NRZ(Non-Return-to-Zero:非ゼロ復帰)直接変調動作を確認しました(4)。さらに、波長多重回路とモノリシック集積した素子による8×56-Gbit/s PAM-4動作を実証しました(5)。また、さらなる低消費電力化と小型化を実現するために、フォトニック結晶を用いたレーザを開発しています(6)。

今後の展開

信号が高速化し伝送容量が増大するにつれて、電気の担っていた部分が光に置き換わり、光がラック間からボード間・ボード内へと入っていきます。これにより、これまで物理サーバ内に閉じ込められていた1つひとつのコンピュータが、ラックスケールでつながった1つのコンピュータになります。このパラダイムシフトを光電融合デバイスで支えるために、一歩ずつ研究開発を進めていきます。

■参考文献

(1) 岡田・木原・岡崎:“IOWNを支えるディスアグリゲーテッドコンピューティング,”NTT技術ジャーナル,Vol. 33,No. 5,pp. 40-44,2021.

(2) 寒川・富澤・岡田・後藤:“オールフォトニクス・ネットワーク,光電融合技術のめざす未来,”NTT技術ジャーナル,Vol. 32,No. 8,pp. 6-9, 2020.

(3) T. Kishi, H. Wakita, K. Shikama, M. Nagatasni, S. Kanazawa, T. Fujii, H. Nishi, H. Ishikawa, Y. Kawajiri, A. Aratake, H. Nosaka, H. Fukuda, and S. Matsuo:“A 25-Gbps×4ch, Low-Power Compact Wire-Bond-Free 3D-Stacked Transmitter Module with 1.3-μm LD-Array-on-Si for On-Board Optics,”OFC 2019, Paper Tu2l.1, San Diego, U.S.A.,March 2019.

(4) T. Fujii, K. Takeda, N-P. Diamantopoulos, E. Kanno, K. Hasebe, H. Nishi, R. Nakao, T. Kakitsuka, and S. Matsuo:“Heterogeneously Integrated Membrane Lasers on Si Substrate for Low Operating Energy Optical Links,”IEEE JSTQE, Vol. 24,No.1, 1500408, 2018.

(5) H. Nishi, T. Fujii, N. P. Diamantopoulos, K. Takeda, E. Kanno, T. Kakitsuka, T. Tsuchizawa, H. Fukuda, and S. Matsuo:“Integration of Eight-Chasnnel Directly Modulated Membrane-Laser Array and SiN AWG Multiplexer on Si,”Journal of Lightwave Technology, Vol. 37, No. 2, pp. 266-273, 2019.

(6) K. Takeda, T. Sato, A. Shinya, K. Nozaki, W. Kobayashi, H. Taniyama, M. Notomi, K. Hasebe, T. Kakitsuka, and S. Matsuo:“Few-fJ/bit data transmissions using directly modulated lambda-scale embedded active region photonic-crystal lasers,”Nature Photonics, Vol. 7,No. 7, pp. 569 – 575, 2013.

(左から)坂本 健/佐藤 昇男/瀬川 徹

光電融合デバイスが通信から演算処理に使われるためには一層の低消費電量・高密度化・低コスト化が必要になってきます。将来版のディスアグリゲーテッドコンピューティングへの適用によりIOWNの世界を実現するようチャレンジしていきます。